台积电在先进制程领先的道路上一往无前,计划3nm技术于2021年进入风险生产、在2022年开始量产,而英特尔的7nm预计最早推出也要到2022年末。

据介绍,相较5nm N5工艺,相同功耗下,台积电3nm N3性能可提高10-15%;相同性能下,N3功耗可降低25-30%;N3的逻辑密度、SRAM密度、模拟密度分别是N5的1.7倍、1.2倍、1.1倍。

同时,台积电总裁魏哲家宣布,台积电已整合旗下包括SoIC、InFO、CoWoS等3D封装技术平台,命名为台积电3D Fabric。

台积电高级副总裁Kevin Zhang和Y.P. Chin在预先录制的视频中提到,台积电正在其总部旁边正建设一个专注于2nm芯片研发的新研发中心,拥有8000名工程师,将运营一条先进的生产线,该项目的第一阶段将于2021年完成。

作为全球晶圆代工“一号玩家”,从台积电的分享,我们可以看到全球先进制程最前沿的芯片制造技术风向。

一、5nm今年下半年见,3nm后年量产

在今天的台积电技术研讨会,台积电介绍了5nm N5、N5P、N4工艺以及3nm N3工艺的PPA优化情况。

据悉,台积电5nm N5工艺广泛采用了EUV技术。相较7nm N7工艺,台积电N5工艺在相同功耗下的性能提高了15%,在相同性能下的功耗降低了30%,逻辑密度为N7的1.8倍。

台积电还提到,N5的缺陷密度学习曲线比N7快,这意味着5nm工艺将比其上一节点能更快地达到更高的良率。

N5P和N4属于5nm N5的增强版本。

N5P主要面向高性能应用,计划在2021年投入使用。与N5相比,同等功耗下,N5P的性能可提高5%;同等性能下,N5P的功耗可降低10%。

由于与N5节点在IP上兼容,因此台积电的5nm N4工艺可提供直接迁移,性能、功耗和密度均有所增强。台积电计划在2021年第四季度开始N4风险生产,目标是在2022年实现大批量生产。

相比5nm N5节点,台积电3nm N3在相同功耗下的性能可提高10-15%,在相同性能下的功耗可降低25-30%;逻辑密度提高70%,SRAM密度提高20%,模拟密度提高10%。

此外,台积电还介绍了专为IoT、移动和边缘设备等低功耗设备而设计的N12e工艺,该工艺是台积电12 nm FinFET节点的增强版,拥有更低功耗、更高性能,支持超低漏电器件和低至0.4V的超低Vdd设计。

#FormatImgID_0#二、英特尔三星“摔跤”,台积电“紧俏”

近来先进制程的战场可谓是波澜起伏,英特尔制程进化再度跳票,三星频传良率不过关,唯有台积电一路喜讯不断,不仅股价持续飙涨,跃居全球第十大市值公司,还迎来制造出10亿颗7nm芯片的新里程碑。

从率先搞定7nm的那一刻起,台积电就成了整个“地球村”的希望。除了三星、英特尔这种自带先进制造厂的IDM巨头,大部分的头部芯片设计公司都跑到台积电7nm的门外排起长队。

原因无他,制程工艺越先进,芯片性能越高、功耗越低,在市场上越有竞争力。

台积电冲得不仅快,良率还高。2018年有超过50款7nm芯片量产,代工方都是台积电。2019年,台积电代工的7nm芯片设计更是超过100种。苹果、高通、华为、英伟达、AMD、赛灵思、联发科等芯片巨头都是台积电7nm的客户。

同时,台积电的7nm N7+工艺是全球第一个在大批量生产中采用EUV的节点,而向后兼容的N6逻辑密度又提高了18%。据台积电介绍,N6具有与N7相同的缺陷密度。

台积电2019年年报显示,这一年,台积电为499个客户生产10761种不同的芯片,在半导体制造领域市场占有率达52%。

从2020年上半年全球前大晶圆代工营收来看,台积电的营收超过2-9名代工营收的总和。

-

浙江杭州夫妻醉酒老公床上酣睡妻子倒挂窗外 提醒:理性饮酒安全第一

头条 22-01-21

-

美国爸爸辅导孩子写汉字气到崩溃一行字写了3小时!网友:这跟国籍无关

头条 22-01-20

-

绝望! 女子隔离14天通过监控看狗子把家拆完 网友:感到“崩溃”

头条 22-01-20

-

辽宁沈阳男子冬天醉卧路边冻掉4根手指!网友:多亏被人发现

头条 22-01-18

-

重庆一孕妇剪毁婚庆店内32件婚纱礼服当事人发文

头条 22-01-17

-

中国空间站与国际空间站一张对比图火了 网友直呼:画面引起舒适

头条 22-01-13

-

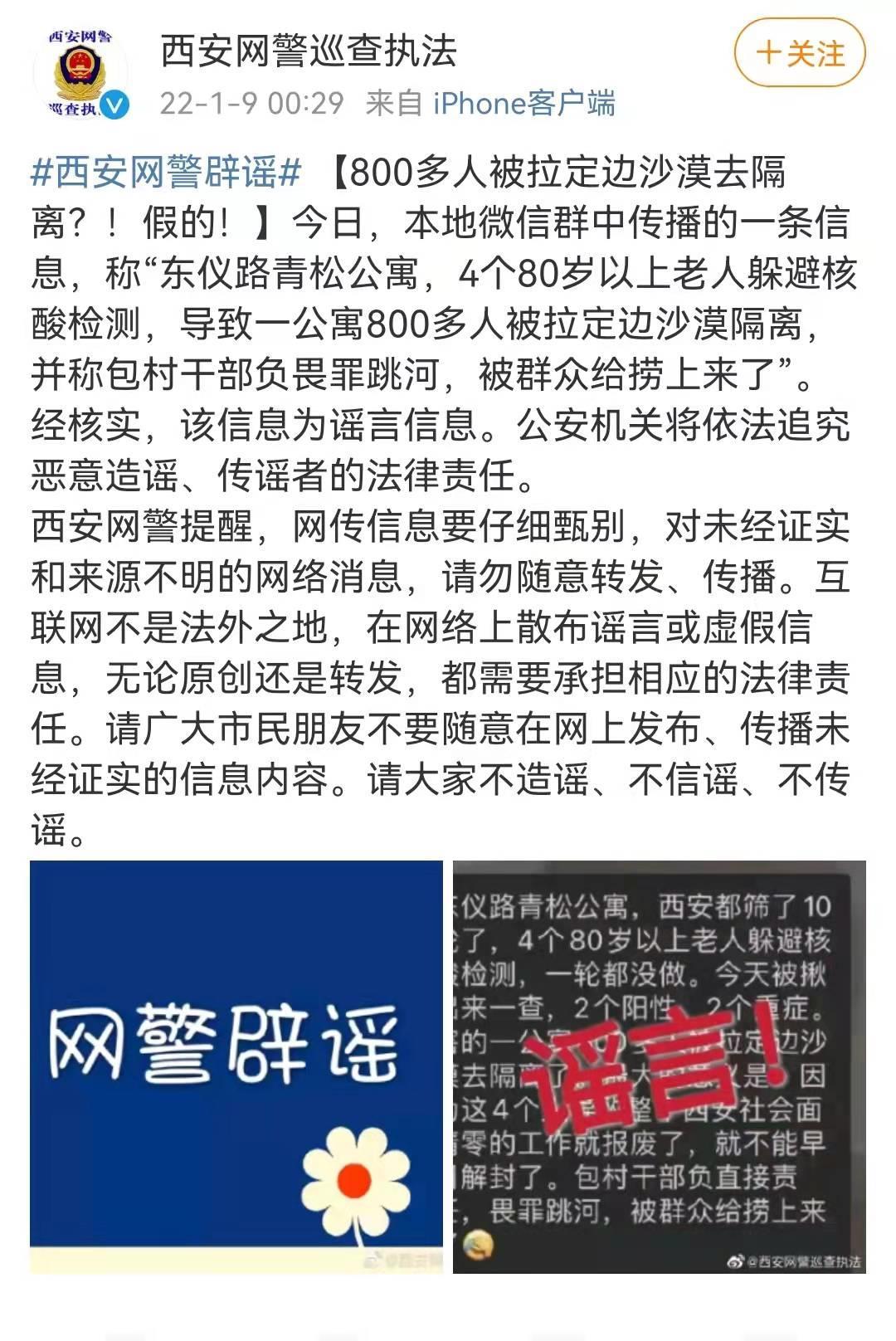

辟谣!800多人被拉定边沙漠去隔离?西安网警:假的!

头条 22-01-11

-

生日蛋糕上插满课本男孩崩溃大哭 妈妈:想提醒他好好复习

头条 22-01-11

-

男子地铁摸女性屁股被扇3分钟耳光?警方通报

头条 22-01-06

-

天津高速现驼鸟奔跑 官方回应:系车主运输途中不慎掉落已被车主领回

头条 22-01-05

-

长得挺特别!菠萝味草莓一斤150元 网友:直接买个菠萝吃不好吗

头条 22-01-05

-

“秦始皇”做核酸珍贵画面流出?逗乐网友!调侃:“秦始皇也要核酸了!”

头条 21-12-31

-

985大学硕士妈妈吐槽儿子是学渣:他爸气得2次心梗!以后只希望孩子健康成长

头条 21-12-31

-

查干湖“头鱼”拍出299.9999万的天价!网友:怎么吃才体现它的身价

头条 21-12-29

-

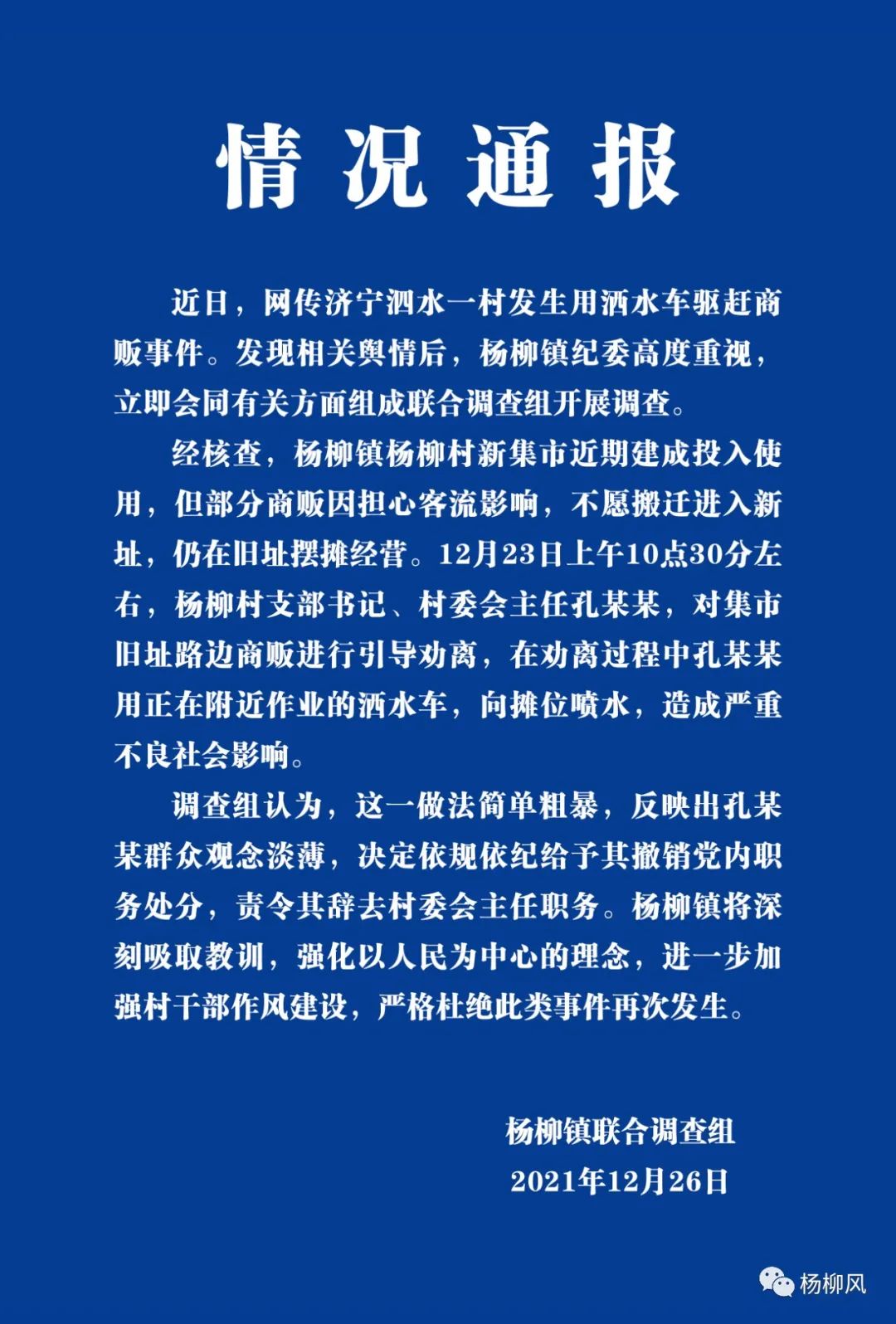

村主任用洒水车向摊位喷水?官方回应:责令其辞去村委会主任职务

头条 21-12-27

-

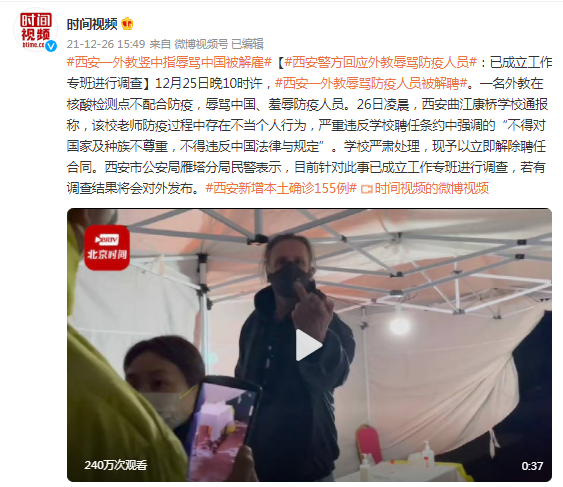

“外教辱骂防疫人员”,西安警方回应:已成立工作专班进行调查

头条 21-12-27

-

破防了!91岁奶奶和8岁猫咪的对话让人泪崩 网友:祝愿老人健康长寿

头条 21-12-23

-

5岁女童配合消防员教科书式自救 网友点赞:很勇敢!

头条 21-12-23

-

大爷被困电梯淡定唠嗑等救援 网友:为大爷的冷静沉着点赞!

头条 21-12-22

-

男子4万元存款18年后却被银行告知存款已被支取仅剩10块钱 法院:银行赔!

头条 21-12-20

-

深圳一男子加油站拔油枪点燃后逃跑 警方已介入调查纵火人员已锁定

头条 21-12-17

-

这位感动千万抖音网友的河南“留虾女孩” 入选央视年度短片《2021看见笑容》

头条 21-12-17

-

泪目!95岁妈妈病床前亲吻74岁生病的女儿 网友:孩子不管多大都是妈妈的宝贝

头条 21-12-15

-

川妹子抽中50颗榴莲直呼吃不完!网友:可以共享你的负担吗?

头条 21-12-15

-

河南省政府发布2022年元旦放假通知

头条 21-12-15

-

濮阳市聚碳新材料产业联盟成立

头条 21-12-15

-

周口机场预计什么时候建好?都有到哪些城市的航线?官方回复来了

头条 21-12-15

-

预计明年超50家企业回归,瑞银称中概股H股上市将继续升温

头条 21-12-15

-

新乡发现一境外输入奥密克戎病例密接者,活动轨迹公布

头条 21-12-15

-

河南:中药配方颗粒不得在医疗机构以外销售

头条 21-12-15

-

中原环保完成发行5亿元超短融,利率2.95%

头条 21-12-15

-

南阳市政府将与中车四方所在新能源装备等领域开展深入合作

头条 21-12-15

-

郑州出台新措施:公租房可“掌上”缴租秒办理

头条 21-12-15

-

国家统计局:11月社会消费品零售总额增长3.9%

头条 21-12-15

-

中国11月规上工业增加值同比增长3.8%

头条 21-12-15

-

1207万!全年就业超额完成预期目标

头条 21-12-15

-

河南凯旺科技公开发行2396万股新股,获6321.47倍申购

头条 21-12-15

-

事关货币政策、房地产、全面注册制,一行两会划定明年工作重点

头条 21-12-15

-

隔夜欧美·12月15日

头条 21-12-15

-

多部委密集部署明年工作!三大看点值得关注

头条 21-12-15

-

立方风控鸟·早报(12月15日)

头条 21-12-15

-

医药巨头今日登陆科创板!高瓴重仓"陪伴",引入"绿鞋"机制

头条 21-12-15

-

皮海洲:临门一脚踏刹车!龙竹科技终止转板说明了什么

头条 21-12-15

-

立方风控鸟·晚报(12月14日)

头条 21-12-14

-

成渝地区双城经济圈建设2022年拟推进160个重大项目,投资约2万亿元

头条 21-12-14

-

总投资额超百亿!中建七局接连中标两个EPC总承包项目

头条 21-12-14

-

2022年部分地方债提前下达,财政提前发力稳经济

头条 21-12-14

-

信阳华信投资集团10亿元中票完成发行,利率3.70%

头条 21-12-14

-

新强联拟择机出售所持明阳智能股票

头条 21-12-14

-

洛阳新强联拟亿元入股山东拟IPO公司,持股4.50%

头条 21-12-14

-

焦作在这场推介会上现场签约28个项目,总投资240亿元

头条 21-12-14

-

河南7种轻微交通违法可免罚

头条 21-12-14

-

广州高校发现古墓考古专业出动!网友:这不巧了嘛!毕业论文自己找来了

头条 21-12-14

-

浙江乐清民警自曝37岁未婚救下轻生女子 网友:一定要最爱自己

头条 21-12-14

-

画面感太强!主人出差猫咪打开水龙头把家淹了 网友:当然是原谅它

头条 21-12-09

- 超全科普!一次看懂北京冬奥15个比赛项目2022-01-24

- 北京地铁4号线陶然亭站、角门西站 人员及2022-01-24

- 广东深圳新增1例境外输入无症状感染者2022-01-24

- 辽宁沈阳新增1例本土无症状感染者 为北京2022-01-24

- 生态环境部:冬奥会期间将对部分污染重、排2022-01-24

- 急寻同乘人员!沈阳本土无症状感染者曾乘坐2022-01-24

- 2021大湾区楼市报告 深圳一手住宅成交量2022-01-24

- “预制菜概念股”得利斯跌停 股价翻一番 2022-01-24

- 5家上市险企2021年保费2.49万亿元 健康险2022-01-24

- 受获准仿制默沙东新冠口服药授权消息提振 2022-01-24

- 科技股互联网股地产股集体走强 香港恒指开2022-01-24

- 热点降温追高风险凸显 两市有别节前暂难表2022-01-24

- 明星基金经理4000字长文详解投资策略 部分2022-01-24

- “十四五”杭州市动漫游戏产业发展成效亮眼2022-01-24

- 全国碳市场累计成交量1.87亿吨 累计成交额2022-01-24

- 中远海能收上交所问询函 要求其补充披露资2022-01-24

- 2021年深市推出股权激励计划和员工持股计划2022-01-24

- 北向资金连续4周净买入 本周5只新股将发行2022-01-24

- 政策注入“强心剂”“十四五”旅游业蓝图绘2022-01-24

- 政策注入“强心剂”“十四五”旅游业蓝图绘2022-01-24

- 2025年环保装备制造业产值力争达1.3万亿元2022-01-24

- 信托公司的盈利能力正在下降 “躺赚”时代2022-01-24

- “留岗红包”密集派发 家政市场正迎来消费2022-01-24

- 深挖热点重点合理加大政策支持 释放居民消2022-01-24

- 2021年我国涉外交易保持活跃跨境资金流动有2022-01-24

- 多地重大项目集中开工 “稳投资”快马加鞭2022-01-24

- 2025年我国绿色消费理念深入人心 绿色低碳2022-01-24

- 去年9省份人均可支配收入涨超10% 2022年新2022-01-24

- 因降雪河南多条高速管制中!京港澳高速新郑2022-01-24

- 想不到,博沃纳做无雾加湿器,竞争对手居然2022-01-24

精彩推荐

阅读排行

- 因冰雪恶劣天气 河南高速禁止车辆上站名单(24日9点50分发布)

- 河南再部署低温雨雪冰冻灾害天气防范应对工作 及时发布预警预报信息

- 速看!河南10部门联合发文:保障务工人员在春节期间安全有序流动

- 今年河南省公路水路计划投资1200亿元以上 新增高速公路通车里程800公里以上

- 河南确保南水北调工程“三个安全” 力争超额完成23.6亿立方米的年度供水计划

- 河南省基本养老保险参保率2025年要达 95%以上

- 注意防范!河南省气象局发布道路结冰黄色预警

- 注意!河南多地明确:全域禁售禁放烟花爆竹

- 提醒!河南省2022年上半年教师资格考试(笔试)1月24日报名

- 河南2022年启动高考综合改革 2025年第一批学生参加新高考